アクセラレータ設計サービス

ネットワーク処理や画像処理など、ハードウェア化することで高速化・低遅延化・低消費電力化を実現します。

SmartNIC/FPGAの柔軟性と適応性を活かし、お客様のシステムに最適な処理アクセラレーションを提供します。

特長

-

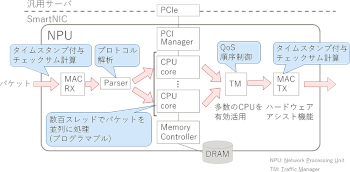

プログラマブルSmartNICの開発

ネットワーク処理ユニットを搭載した先進的なデバイスであるSmartNICのファームウェア開発が可能です。 -

DPDK/eBPF/XDP等アプリケーションの開発

DPDK(Data Plane Development Kit)等を用いたソフトウェアベースのネットワーク処理高速化開発が可能です。 -

FPGA方式検討・論理設計/検証

要求機能/性能の詳細化・方式検討・実装検討から、回路設計・検証、実機評価まで実施可能です。

サービス詳細

概要

-

SmartNIC/DPDKソフトウェア開発サービス

SmartNICの採用に向けた単体評価から、OVSオフロードやNVMe-oFなどの機能を活用するための構成および設定検討、システム試験まで、SmartNIC導入によるお客様のシステム目標の実現をサポートいたします。さらに、SmartNICファーム開発や、DPDK/XDPを用いたソフトウェアベースのネットワーク処理アプリケーション開発を通して、お客様のカスタムニーズに応じた技術サービスも提供いたします。お気軽にお問合せ下さい。 -

FPGA開発サービス

FPGAを用いた画像処理・ネットワーク処理開発など、お客様のカスタム要件に応じた技術サービスを提供いたします。当社のFPGA開発サービスにより、お客様独自の機能を実現し、アプリケーションの性能を向上させることができます。

得意分野

- やわらかい状態の要求仕様から、方式検討・デバイス選定まで、培ってきた経験を活かしお客様と共に明確化

- コスト最適、性能最適など、ご要望に合わせた方式を検討可能

- DPDK, eBPF/XDP, P4などを用いた、ハードウェアアーキテクチャを理解・考慮したネットワーク処理プログラミング

- SmartNICを用いたサーバサイドの高精度時刻同期(PTP)関連技術

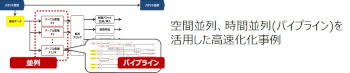

- FPGA開発におけるメモリ構成/データフォーマット最適設計、並列化等データパス最適化による高速処理

適用例

- SmartNIC, FPGAを用いたパケットジェネレータ・アナライザ開発

- DPDKを使用したパケットキャプチャ、ネットワーク解析ソフトウェア開発

- 各種環境構築・性能測定: OVSオフロード、NVMe-oF、RDMA、GPU-Direct、サーバ時刻同期(PTP,GNSS)、等

SmartNIC向けに設計した

パケットジェネレータ/アナライザ構成

パケットジェネレータ/アナライザ構成

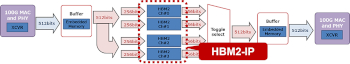

HBM2-IP活用事例:W/Rあわせて400Gbps物理帯域確保

FPGA論理開発:通信で培った設計技術を活用

エンジニアの声

アクセラレータ設計サービス

ソフトウェアの柔軟性とハードウェアの高速性をうまく活かした設計(アーキテクチャ最適化)をすることで、性能向上や低消費電力化を実現します。検討段階からお客様と一緒に進められますので、お気軽にお問い合わせください。